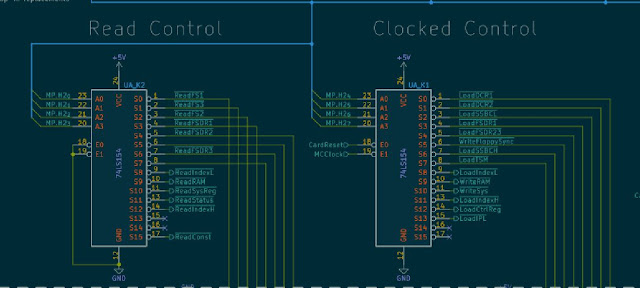

These are used to select various registers in the drive control hardware. These are used to read status and data from the drive.

0 = ReadFS1

1 = ReadFS3

2 = ReadFS2

3 = ReadFSDR1

4 = ReadFSDR2

6 = ReadFSDR3

This input reads the DMA status

11 = ReadStatus

These are used to access the internal RAM on the board. To read the RAM the address you want to reads needs to first be put in the memory index register then the ReadRAM input can be used to read the data. ReadIndexL and ReadIndexH can be used to read back the contents of the index register.

8 = ReadIndexL

12 = ReadIndexH

9 = ReadRAMThis inputs reads the System Register which is used by the FFC to communicate with the rest of the system.

10 = ReadSysReg

Finally this input reads from the Constant ROM. Unlike a normal CPU, the FFC's CPU cannot included data as part of an opcode so this is used to provide constant data to the CPU.

15 = ReadConst

On the write selector the enables are connected to MCClock and MasterReset. MCClock is the master clock so it probably needed for the proper timing of the writes. MasterReset is probably used to prevent spurious writes when the board is starting up. The signals connected to the write outputs are as follows:

This set of signals control writes to drive control registers.

0 = LoadDCR1

1 = LoadDCR2

2 = LoadSSBCL

3 = LoadFSDR1

4 = LoadFSDR23

5 = WriteFloppySync

6 = LoadSSBCH

7 = LoadTSM

This one loads the DMA control register

12 = LoadCtrlReg

These signals control access to the internal RAM. Just like for read, the address to write two must first be written to the Index registers and then the RAM can be written to using WriteRAM.

8 = LoadIndexL

11 = LoadIndexH

9 = WriteRAM

I believe this output is used to trigger interrupts to the main processor in the system.

13 = LoadIPL

This output writes to the System Register which is used by the FFC to communicate with the rest of the system.

10=WriteSys

These two outputs are unconnected so can be used for instructions where not output is needed.

14=No connection

15=No connection